NEWS | 新闻

• Aug. 30, 2024, The paper "L Wang, F Xie, J Liu, T Liu, L Peng, Z Zhang, T Wei, R Chen, Power and Thermal Integrity Analysis of High Performance and Low Power CPUs at Sub-2nm Node Designed with Various Advanced Backside PDNs" is accepted by IEDM 2024

• Aug. 22, 2024, Invited talk by the Institute of Computing Technology, Chinese Academy of Sciences on "CNT-based 3D Integrated Circuits and Systems", at Summit Forum of State Key Lab of Processors, ICT, CAS

• Jul. 22, 2024, Invited talk by Institute of Electronic Design Automation, Peking University on "Technology and Design of 3D IC", at IC Summer School on Advanced Technology 2024

• May. 29~31, 2024, ECTC 2024 paper "F Xie, R Chen, et al, Thermal mitigation strategy for backside power delivery network" is published.

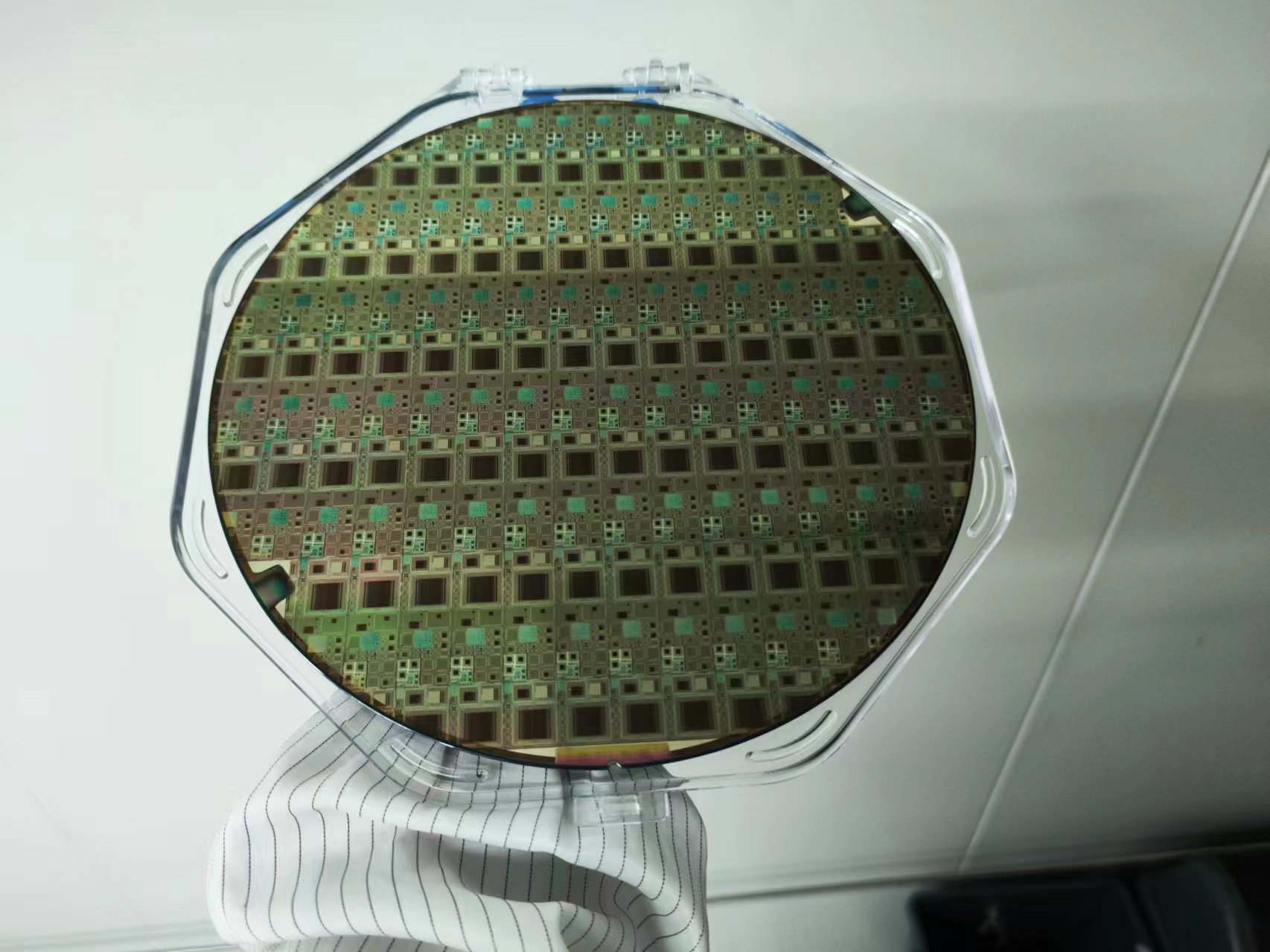

• May. 14, 2024, The team's first CNT Silicon heterogeneous chip comes back from the factory, preparing for the CNT process.

• Oct. 13, 2023, Congratulations to Prof.Chen on being selected for the 2023 National Overseas High Level Youth Talent Program

• Jul. 26, 2023, The view "Pushing carbon nanotube circuits below the 10-nm node" (Prof.Chen, the only author) is published on Nature Electronics, which is commenting on the paper "Scaling aligned carbon nanotube transistors to a sub-10 nm node"

• Jul. 21, 2023, Invited paper submitted by Anabela (IMEC) to IEDM 2023 (Prof.Chen, 3rd co-author, contributed to the paper with backside power delivery modeling and backside clock study)

• Jul. 01, 2023, Prof.Chen joined School of Electronics, Peking University

• Jun. 27, 2023, Prof.Chen left IMEC

• Jun. 11, 2023, Symposium on VLSI Technology and Circuits 2023 Workshop (highest attendance of all 6 workshops) organized by Prof.Chen: Towards Functional Backside: What’s next after Backside Power Delivery? Workshop 3 | Symposium on VLSI Technology and Circuits (vlsisymposium.org)

• Jan. 05, 2023, The IEDM 2022 paper (R. Chen et al, Power, Performance, Area and Thermal Analysis of 2D and 3D ICs at A14 Node Designed with Back-side Power Delivery Network) was interviewed and reported by IEEE Spectrum: https://finance.sina.com.cn/tech/roll/2023-01-05/doc-imxzcerp5808137.shtml

• Nov. 03, 2022, Invited talk at Proceedings of the 24th ACM/IEEE Workshop on System Level Interconnect Pathfinding: Opportunities of Chip Power Integrity and Performance Improvement through Wafer Backside (BS) Connection: https://dl.acm.org/doi/10.1145/3557988.3569716

• Jun. 13~17, 2022, VLSI 2022 paper (R. Chen et al, Backside PDN and 2.5 D MIMCAP to Double Boost 2D and 3D ICs IR-Drop beyond 2nm Node) is selected as Technology focus paper: https://archive.vlsisymposium.org/22web/program/schedule-at-a-glance/

• Jun. 13~17, 2022, VLSI 2022 paper (A Veloso, A Jourdain, D Radisic, R Chen, et al, Scaled FinFETs Connected by Using Both Wafer Sides for Routing via Buried Power Rails) is selected as Technology highlight paper: https://archive.vlsisymposium.org/22web/program/schedule-at-a-glance/

• May. 05, 2022, Invited talk by Prof. H.S. Philip Wong (Stanford University) on paper TVLSI (R. Chen, et al. Carbon Nanotube SRAM in 5-nm Technology Node Design, Optimization, and Performance Evaluation—Part I: CNFET Transistor Optimization)

• Dec. 13, 2021, IEDM 2021 paper (R. Chen, et al, Design and optimization of SRAM macro and logic using backside interconnects at 2nm node) reported by ssSILICON: Imec demonstrates significant performance gains utilizing backside 3D SOC interconnects - News (siliconsemiconductor.net) and highlighted by imec: IEDM 2021 | imec (imec-int.com); recommended and cited by Samsung: Samsung uses BSPDN technology for 2nm chips, improving performance by 44% and efficiency by 30% - TechGoing

• Jun. 13, 2021, Symposium on VLSI Technology and Circuits 2021 Workshop organized by Prof.Chen: PPAC Analysis and System-Technology Co-Optimization for 3D Memory-on-Logic IC, Many-Core SOC and AI Computing Applications: Workshop 2 | Symposia on VLSI Technology and Circuits (vlsisymposium.org)

• Feb. 10, 2021, Invited presentation to Intel “Back Side Metal Routing based SRAM Macro Design and Optimization”

• Feb. 16, 2021, Invited presentation to Intel “3D-optimized SRAM Memories for iN5/iN3: Update on Macro Design and Impact on Memory-on-Logic Systems”

• Dec. 13, 2020, IEDM 2020 paper (R. Chen, et al, 3D-optimized SRAM macro design and application to memory-on-logic 3D-IC at advanced nodes) the 3D memory-on-logic technique was adopted (or used just by chance?) by AMD product 3D Vcache: AMD 3D V-Cache™ Technology | AMD