Research | 研究

Research Achievements | 代表成果

◈ 挑战芯片存储墙难题:集成电路设计-工艺协同优化

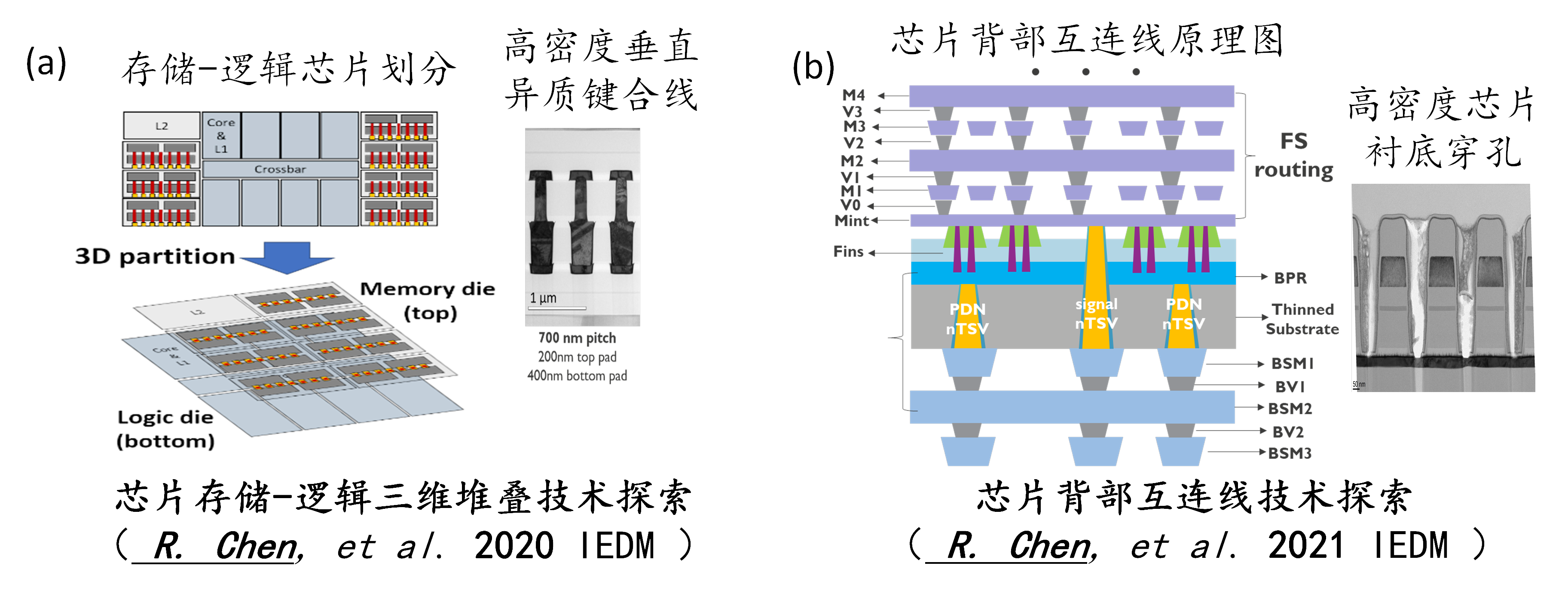

提出片上存储-逻辑堆叠的三维芯片设计方案,并利用 3nm 工艺节点设计三维芯片,并证明相比二维芯片有高达 70% 的性能提升。成果发表于 IEDM 2020。

提出先进的芯片背部互连线技术,优化芯片的全局信号设计,例如时钟信号、存储宏单元的全局信号线等。芯片正面后端互连线用于高密度信号线互连而芯片背部互连线用于长程信号互连,从而实现优势互补,整体上提高芯片的互连效率和速率,有效提高芯片的性能并降低功耗。成果发表于 IEDM 2021。

相关的研究成果已经得到英特尔、高通(Qualcomm)等顶尖半导体公司的关注并受邀作技术报告,得到高度的评价。同时工作还受到包括 eeNews 和 ssSILICON 在内的欧洲多家半导体媒体报道。

欧盟玛丽居里项目“三维芯片设计及研究”获得欧盟权威项目评审专家高度认可,项目的技术和影响力两大指标均获满分.

◈ 克服芯片功耗墙难关:芯片背部供电技术

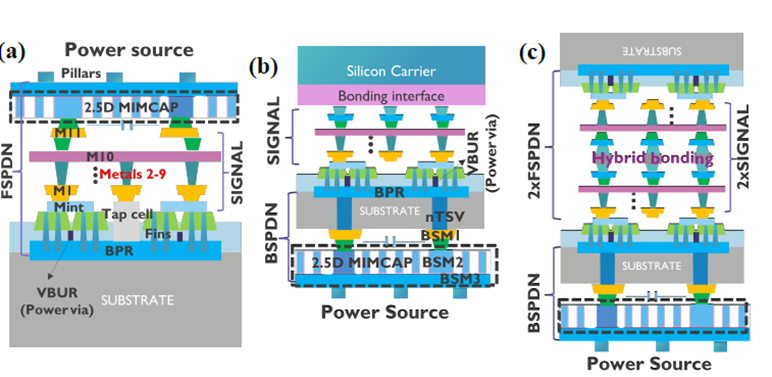

把芯片背部互连线技术应用到芯片内部电源网络的设计当中,形成芯片背部供电能力。把芯片的局域低层金属直接与芯片背部的全局互连线(大尺寸、低电阻率)高效互连,从而有效降低芯片的片内电压降,并提高芯片的布局布线能力和综合性能。成果发表于 IEDM 2022。

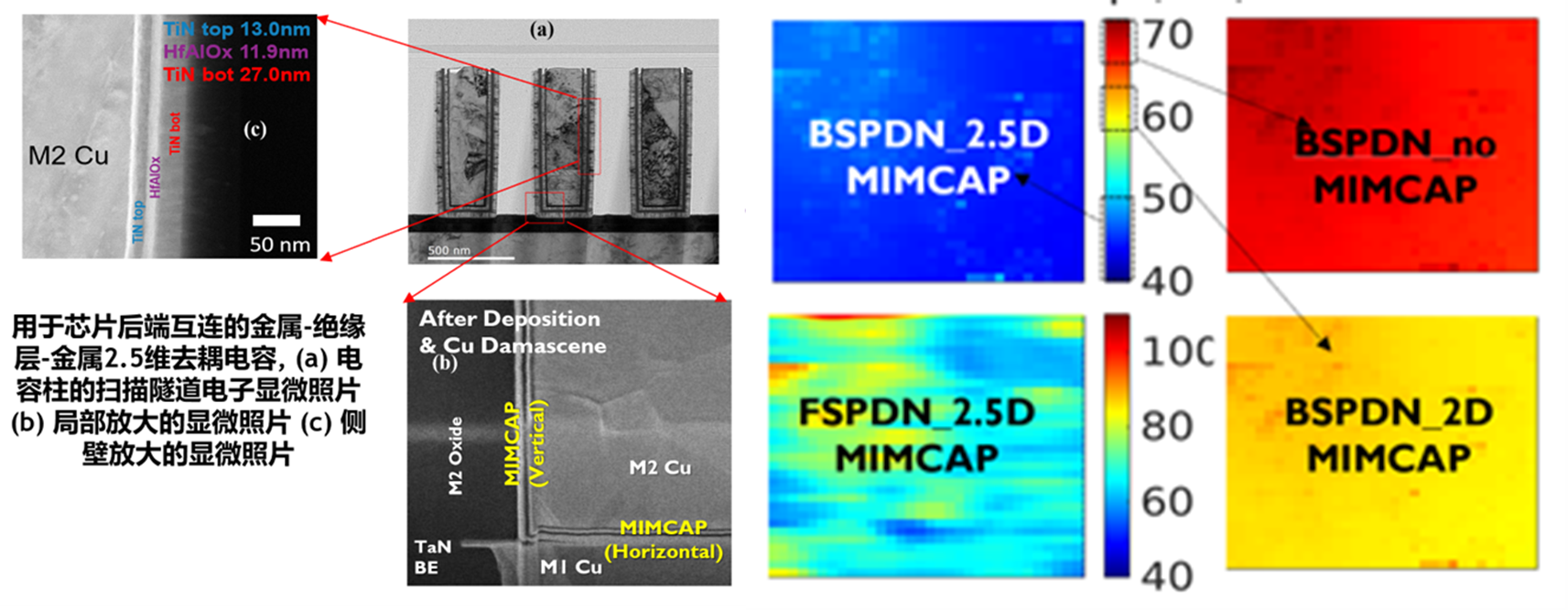

通过工艺集成,在后端互连线内集成了准三维(2.5维)的金属-绝缘层-金属的去耦电容,这种电容相比传统的二维金属-绝缘层-金属电容有高达7倍的电容密度提升。结合芯片背部供电技术,可以实现芯片片内电压降的有效降低,克服芯片功耗墙难题。成果发表于VLSI 2022。

相关工作的四篇论文(陈荣梅教授作为两篇一作、两篇共同作者)发表于 Symposium on VLSI 2022 和 IEDM 2022。其中两篇文章分别被选为 VLSI 大会重点技术介绍文章、大会技术亮点文章。IEDM 2022的工作也得到了 IEEE 旗舰杂志 IEEE Spectrum 高级编辑 Samuel K. Moore 的正面采访和报道,充分认可了相关工作的重要性与创新性。在工业界层面,相关工作得到了包括英特尔、三星、台积电、ARM、华为等全球知名半导体公司的高度关注,数次被邀请做相关技术报告。

◈ 走出互连线压缩困境:碳纳米管互连线的鲁棒性研究

从器件物理建模入手,全面分析碳纳米管加工工艺中离子掺杂水平、缺陷和碳纳米管直径大小的涨落对碳纳米管互连线电学参数的影响,并首次将这些参数变化对碳纳米管集成电路性能、功耗和可靠性的影响表征出来。相关成果发表于TED 2018。

创新性地提出和设计了基于碳纳米管晶体管+碳纳米管互连线的全碳纳米管SRAM电路模块,并给予功耗、密度和性能的设计优化。证明相比当前产业界最先进的 SRAM 模块,全碳纳米管 SRAM 在功耗和集成密度上具有显著的优势,并且具有可比拟的性能。

相关成果两次以姐妹篇文章连载的形式在 IEEE Transactions on Electron Devices (TED)和 IEEE Transactions on Very Large Scale Integration Systems (TVLSI)上发表了四个原创工作(陈荣梅教授作为第一作者兼通讯作者),并在国际知名学术会议DATE上作学术研讨。斯坦福大学的 H.S. Philip Wong 教授(IEEE Fellow, 曾是 IEDM 和 Sympoisa on VLSI 两大顶会的执行主席)对相关工作表示出高度的兴趣,并且特别邀请陈荣梅教授作学术报告。

Research Target | 研究目标

实验室研究聚焦三维碳基-硅基异质集成设计及类脑计算探索,包括:

◈ 器件建模——碳纳米管 PDK 和标准单元库建立

◈ 电路设计——三维异质集成方法及工艺技术

◈ 应用探索——三维碳基硅基异质集成类脑计算探索

Research Interests | 研究方向

◈ 大规模碳基集成电路设计和优化

建立碳纳米管晶体管及集成电路的标准工艺库(PDK)和单元库等软件平台。PDK 包括碳纳米管晶体管电学模型、版图设计标准和寄生参数提取规则文件。单元库则是大规模集成电路设计时所需要的基础单元,包括反相器、与非门、触发器等。

综合物理规律分析和实验现象描述,开发碳纳米管晶体管模型,保证模型的精确度和准确度,有助于从物理分析角度进一步优化碳纳米管的性能和工艺,使碳纳米管的模型开发和工艺的改良形成正反馈的回路

◈ 三维碳基硅基异质集成方法及工艺技术

针对异质(碳基硅基)的三维集成电路,开发电路设计方法(EDA工具和电路设计技术),保证上下层芯片间一体化优化的需求。

开展一定的工艺探索,利用体硅穿孔(TSV)技术或者异质键合线(hybrid bonding)实现高密度、低寄生参数的垂直互连。

◈ 三维碳基硅基异质集成对芯片计算架构的影响

探索三维堆叠设计的类脑计算,把类脑计算中存储模块垂直放置在计算模块的上面,通过垂直互连线有效增加逻辑和存储的带宽,同时降低其互连距离,从而解决存储读取瓶颈(memory-wall)的问题。