新闻 | News

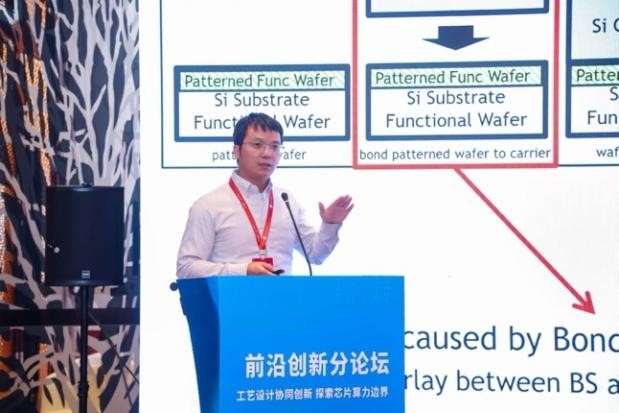

• 2025年12月20号,陈荣梅教授主持了HiPi Chiplet论坛“前沿创新”分论坛,并受邀作《芯片背部供电和背部信号互连技术》技术报告

• 2025年12月4日,陈荣梅教授邀请了中国科学院计算技术研究所副所长、处理器芯片全国重点实验室主任、中国计算机学会体系结构专委会主任陈云霁应邀作题为《从人工智能到处理器芯片》的学术报告。彭练矛院士和陈荣梅教授共同为陈云霁研究员颁发讲座纪念牌

• 2025年11月15日,陈荣梅教授受邀参加长鑫存储组织的论坛《集成电路与人工智能融合创新研讨会》并且作芯片背部供电技术的学术报告

• 2025年10月25日陈荣梅教授受邀参加华为主办的《破挑战、启新程:智能时代计算商片的创新与未来》圆桌论坛,探讨背部供电和三维集成技术对国内自主可控半导体技术发展的重要作用。团队与华为图灵Fellow廖博士及其核心技术团队进行深入技术探讨,并拟定合作计划

圆桌论坛环节

圆桌论坛环节

与华为图灵Fellow廖博士合影

与华为图灵Fellow廖博士合影

与华为图灵核心技术团队合影

与华为图灵核心技术团队合影

• 2025年9月,两篇团队文章+一篇与香港中文大学合作文章被DATE 2026会议接受。分别是:

[1]Y. Wang*, X. Liu*, H. Zhou*, …, R. Chen, Evaluation of Thermal and Power integrity and its impact on Performance for 3D Memory-on-Logic CPUs with FSPDN and BSPDN

[2]H. Zhou, H. Yang, X. Liu, …, R. Chen Architecture and Technology Co-optimization for 3D ICs with Advanced Backside PDN Considering Power Integrity and Thermal Integrity Impact

[3]Chenghan Wang, Zhen Zhuang∗, Kai Zhu, Darong Huang, Luis Costero, Rongmei Chen*, David Atienza, TsungYi Ho, ETLA-3D: Equivalent Thin Layer Aggregation based Thermal FEM for Hybrid Bonding F2F 3D ICs

• 2025年8月,团队与清华大学唐建石老师合作文章被IEDM 2025会议接受。

Yijia Fan, Jianshi Tang*, Yanbo Su, Hu Zhou, Rongmei Chen*, Xiaosen Liu*, et al. High-Performance IGZO-based DrMOS with Vertical Channel Power Transistor for Monolithic 3D Integrated Active PDNs with On-Chip Voltage Conversion

• 2025年2月,团队正式启动由课题组牵头承担的《碳基处理器芯片技术研究》和《晶圆级脉冲神经网络芯片技术研究》两项国家级重点研究项目。

• 2024年08月30日,团队文章"L Wang, F Xie, J Liu, T Liu, L Peng, Z Zhang, T Wei, R Chen,

Power and Thermal Integrity Analysis of High Performance and Low Power CPUs at Sub-2nm Node Designed with Various Advanced Backside PDNs"被IEDM 2024会议接受

• 2024年08月22日,受中国科学院计算技术研究所邀请,陈荣梅教授在处理器芯片全国重点实验室第二届前沿高峰论坛上做题为“碳基三维集成电路和系统”的报告

• 2024年07月23日,受无锡北京大学EDA研究院邀请,陈荣梅教授在2024年“集成电路先进技术暑期学校”上做题为“先进三维集成电路工艺以及设计进展”的报告

• 2024年05月29-31日,团队文章"F Xie, R Chen, et al,

Thermal mitigation strategy for backside power delivery network"被发表于 ECTC 2024 会议上

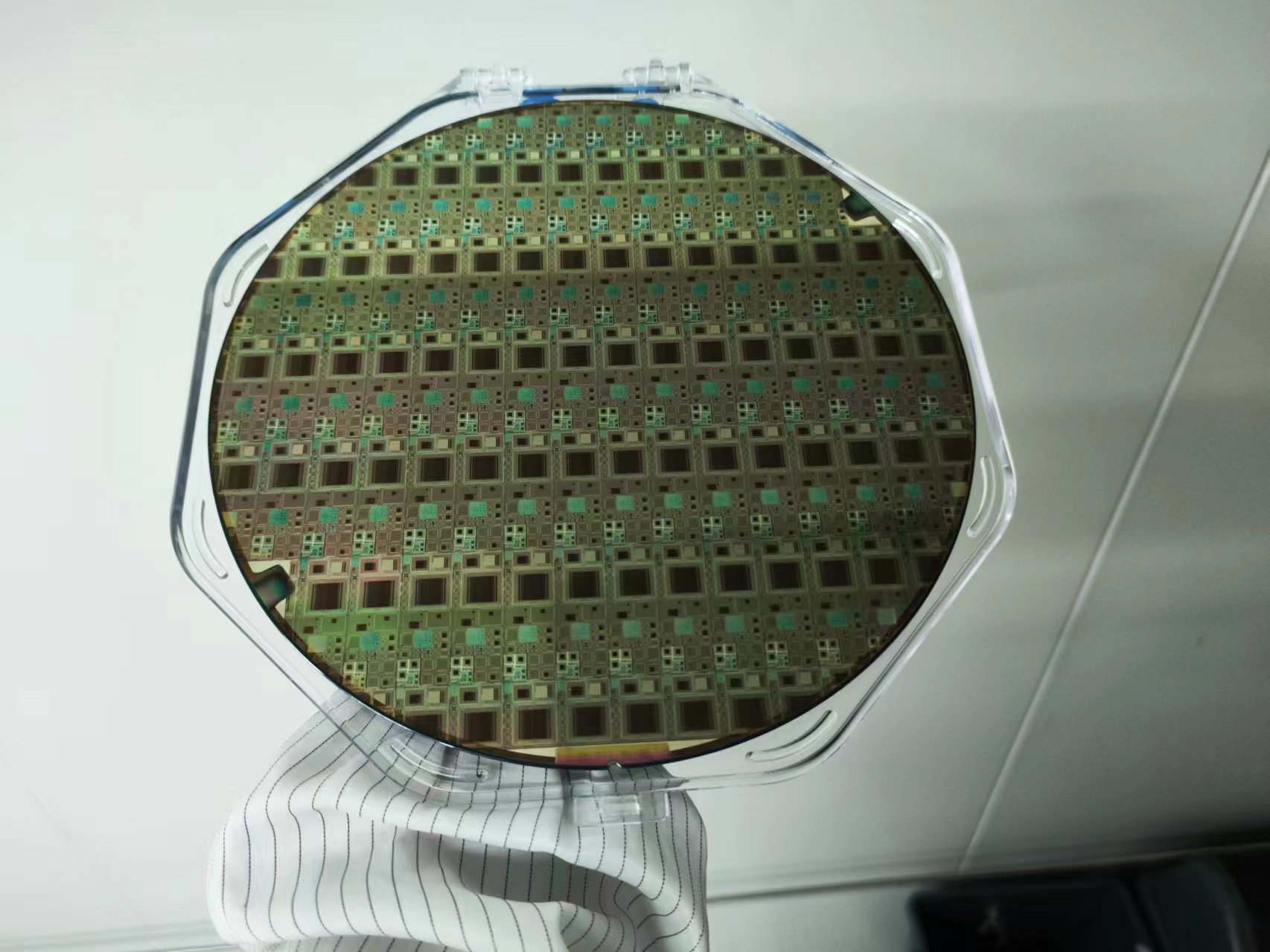

• 2024年05月14日,团队第一块碳硅异质集成芯片已完成流片,准备进行碳基工艺

• 2023年10月13日,恭喜陈荣梅教授入选2023年国家海外高层次青年人才项目

• 2023年07月26日,评论文章 "

Pushing carbon nanotube circuits below the 10-nm node"(陈荣梅教授作为唯一作者)发表于 Nature Electronics,文章评论了论文"

Scaling aligned carbon nanotube transistors to a sub-10 nm node"

• 2023年07月21日,受邀文章被提交至 IEDM 2023(陈荣梅教授作为第三作者,主要贡献是设计了芯片背部供电的模型,并研究了背面时钟相关问题)

• 2023年07月01日,陈荣梅教授正式作为助理教授加入北京大学电子学院

• 2023年06月27日,陈荣梅教授离开欧洲微电子研究中心(IMEC)

• 2023年06月11日,在 Symposium on VLSI Technology and Circuits 2023 会议中,陈荣梅教授组织的研讨会,“芯片背部能实现的功能——背部供电技术之后的技术可能”,获得了全部6个研讨会中最高的参与度:

Workshop 3 | Symposium on VLSI Technology and Circuits (vlsisymposium.org)

• 2023年01月05日,文章"R. Chen et al,

Power, Performance, Area and Thermal Analysis of 2D and 3D ICs at A14 Node Designed with Back-side Power Delivery Network"

被 IEEE Spectrum 杂志采访并报导:

https://finance.sina.com.cn/tech/roll/2023-01-05/doc-imxzcerp5808137.shtml

• 2022年11月03日,在第24届 ACM/IEEE 关于系统级互连路径搜索的研讨会上,陈荣梅教授受邀报告:通过晶圆背面(BS)连接提高芯片电源完整性和功率性能的可能:

https://dl.acm.org/doi/10.1145/3557988.3569716

• 2022年06月13-17日,文章(R. Chen et al,

Backside PDN and 2.5 D MIMCAP to Double Boost 2D and 3D ICs IR-Drop beyond 2nm Node

)被发表于 VLSI 2022 会议上,并被遴选为技术关注文章:

https://archive.vlsisymposium.org/22web/program/schedule-at-a-glance/

• 2022年06月13-17日,文章(A Veloso, A Jourdain, D Radisic, R Chen, et al,

Scaled FinFETs Connected by Using Both Wafer Sides for Routing via Buried Power Rails

)被发表于 VLSI 2022 会议上,并被遴选为技术亮点文章:

https://archive.vlsisymposium.org/22web/program/schedule-at-a-glance/

• 2022年05月05日,受斯坦福大学 H.S. Philip Wong 教授邀请,陈荣梅教授报告分享了发表在 TVLSI 会议的文章(R. Chen, et al.

Carbon Nanotube SRAM in 5-nm Technology Node Design, Optimization, and Performance Evaluation—Part I: CNFET Transistor Optimization

)

• 2021年12月13日,文章(R. Chen, et al,

Design and optimization of SRAM macro and logic using backside interconnects at 2nm node

)被发表于 IEDM 2021 会议,并被 ssSILICON 媒体报导:

Imec demonstrates significant performance gains utilizing backside 3D SOC interconnects - News (siliconsemiconductor.net)

。同时该文章也被 IEDM 2021 会议列为亮点文章:

IEDM 2021 | imec (imec-int.com)

;三星公司推荐并引用了该文章:

Samsung uses BSPDN technology for 2nm chips, improving performance by 44% and efficiency by 30% - TechGoing

• 2021年06月13日,Symposium on VLSI Technology and Circuits 2021 会议上,陈荣梅教授组织了研讨会:逻辑 IC、多核 SOC 和 AI 计算应用上3D存储器的 PPAC 分析和系统技术协同优化:

Workshop 2 | Symposia on VLSI Technology and Circuits (vlsisymposium.org)

• 2021年02月10日,陈荣梅教授受邀前往英特尔公司做题目为“基于背面金属布线的 SRAM 计算单元设计与优化”的报告

• 2021年02月16日,陈荣梅教授受邀前往英特尔公司做题目为“用于 iN5/iN3 的3D优化 SRAM 存储器:计算单元设计的更新和对逻辑系统存储器的影响”的报告

• 2020年12月13日,发表于 IEDM 2020 的文章(R. Chen, et al,

3D-optimized SRAM macro design and application to memory-on-logic 3D-IC at advanced nodes

)中,3D存算一体技术被(巧合地)应用在了 AMD 公司的新产品 3D Vcache 上:

AMD 3D V-Cache™ Technology | AMD